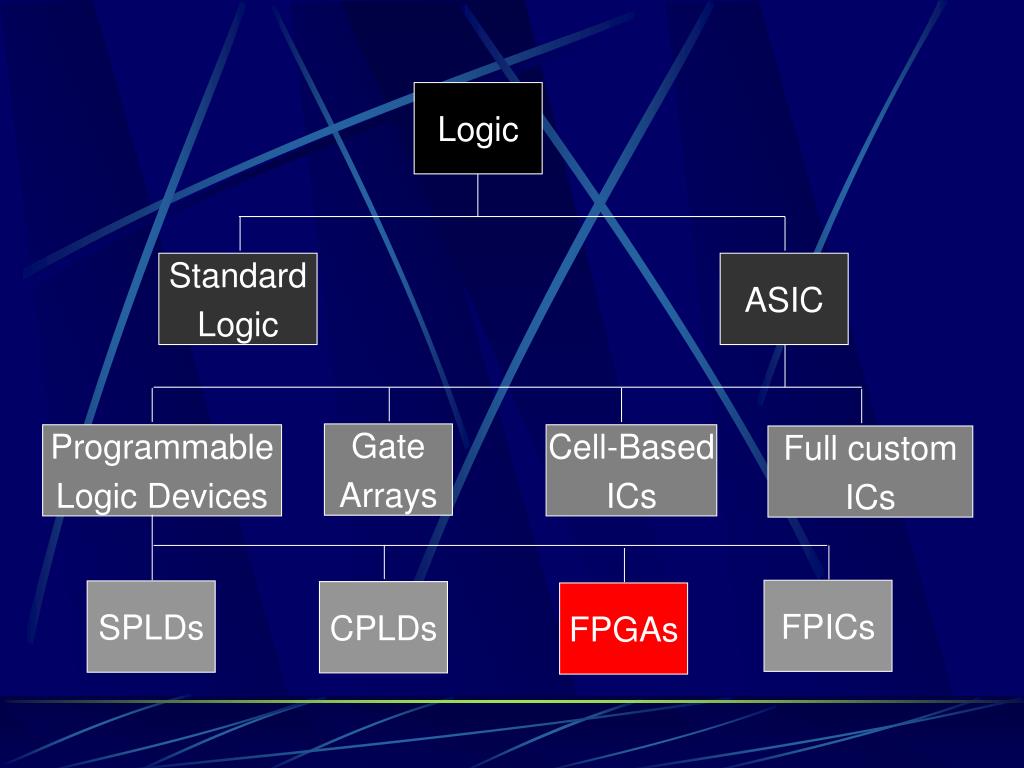

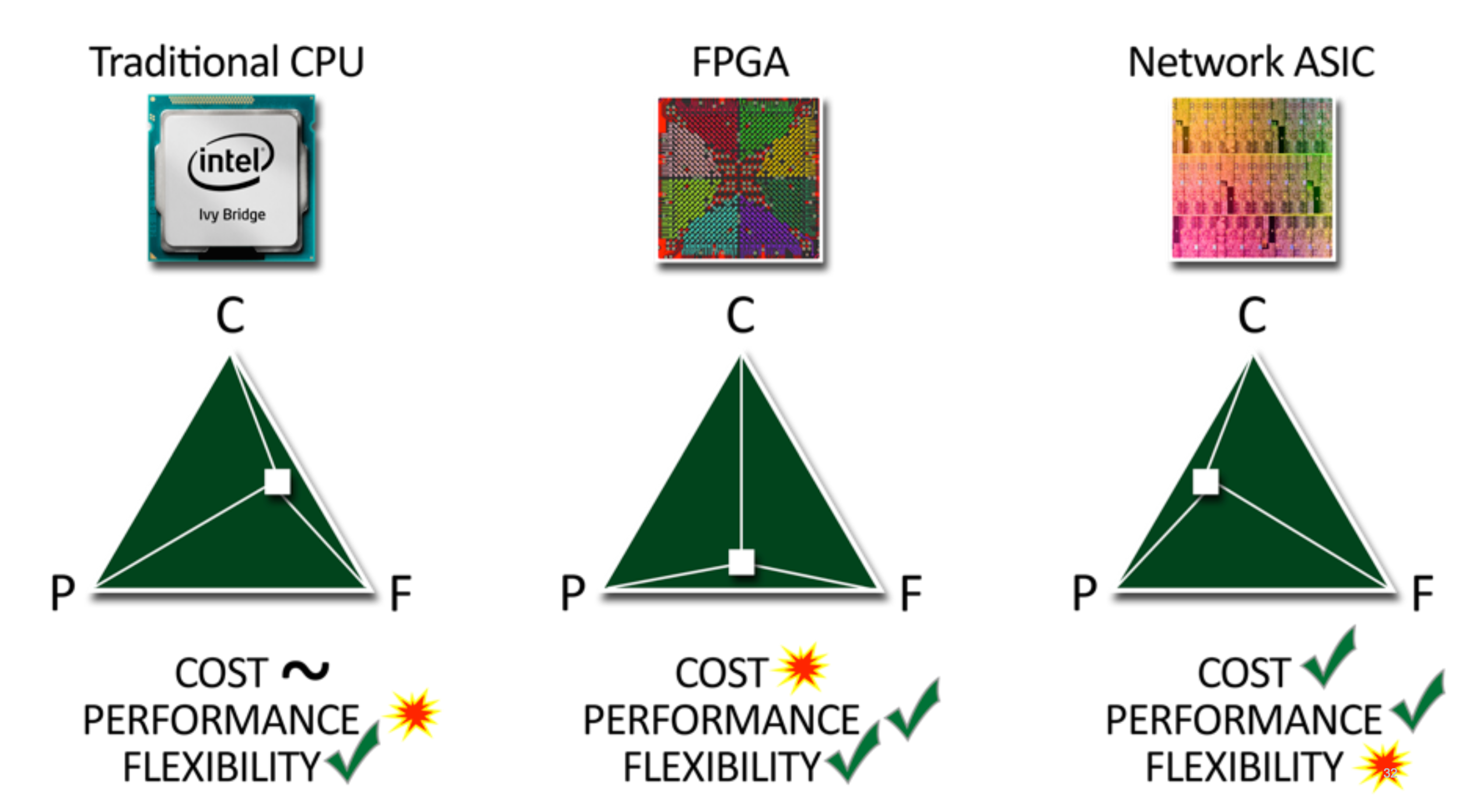

CLB (Configurable Logic Block) includes digital logic, inputs, outputs.The functions of an FPGA architecture module are discussed below: The basic FPGA architecture has two dimensional arrays of logic blocks with a means for a user to arrange the interconnection between the logic blocks. They are I/O blocks or Pads, Switch Matrix/ Interconnection Wires and Configurable logic blocks (CLB). The general FPGA architecture consists of three types of modules. Therefore, these are used in VLSI based projects for electronic engineering students. FPGAs are some of the new trending areas of VLSI. This article describes about theFPGA basics and FPGA architecture module that includes I/O pad, logic blocks and switch matrix. But, FPGAs are fabricated in less than a second,the cost will be from a few dollars to a thousand dollars.The flexible nature of the FPGA comes at a significant costin area, power consumption and delay.When compared to a standard cell ASIC, an FPGA requires 20 to 35 times more area, and the speed’s performance will be 3 to 4 times slower than the ASIC. Normally, ASICs takes months to manufacture and the cost of them will be thousands of dollars to obtain the device. whereas the one you build by yourself will be more personal and you will have to do the math on its performance, complexity and bulkiness.FPGAs can provide a number of advantages over a fixed function ASIC technology such as standard cells. Indeed nand gates are the building block of digital electronics, because from them you can bassically design every other device, but the design normally changes and may be simplified or enlarged depending on the application, wheather it is for power, communications, data storage, etc.įinally, as you said a RAM can be build form D FF's, but once again, the main difference between building one by yourself and usign an Integrated Circuit, is that the IC has been previously designed for an application in frecuency, power, simplicity, price, etc. Similarly with flip flops, muxes and so much other devices. Thus I bet that the digital design of logic elements is more extensive (consider also FET's which may have different configurations). Some simple rule such as "when the number of bits is < then.", "when the depth is <, then." etc.īuilding half gates from a NAND gate considering its transistor count is not always correct, from the next picture you can see that there is only one transistor and four diodes.

In my designs I often consider small memories such as 64x8 or 128x16 and I'd really like to understand when one method is better than another. I assume that there's some overhead here. From the above, RAM cells seem so much better but I remember a friend of mine telling me years ago, for a 256x8 RAM that "it wasn't worth it, might as well doing it with FFs". RAMs cell = 6T/bit = 1.5 gates/bit, dual port = 8T = 2 gates/bit RAMs made with D FFs => 7-10 gates/bit + suitable muxes (see above).

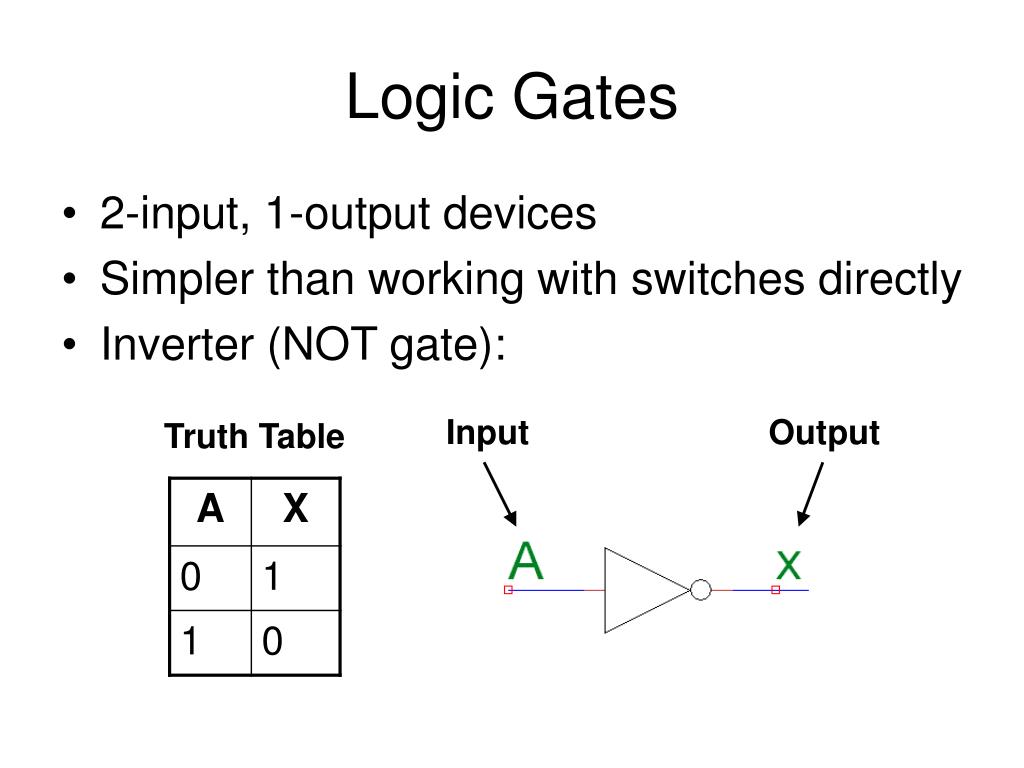

How do I extend this to multiple input muxes ? What's the trade off with gate muxes ?įrom this discussion, muxes tend to be transmission gate.Įnabled, synchronous D FF = D FF + MUX2_1 = 6 + 4 = 10 gates, 6 + 1 (transmission gate mux) = 7 gates, 6 + gated clock = 7 gates ? Which one is more common ? Mux 2:1 with transmission gates = 4 T = 1 gate If anyone has some more data points for MUX 4:1, 8:1, 16:1, etc Multiple input muxes can be built from MUX2_1 or with multiple input NANDs (see above) MUX 2 :1 = 4 gates or 3 NAND2 + NOT = 3.5 gates ? N inputs NAND = 2*N T = N/2 gates ? Max reasonable N ? Two input AND = NAND2 + NOT = 1.5 gates ? Two input NAND (NAND2) = 4 T(ransistors) = 1 gate

FPGA LUT TO ASIC GATES FREE

Please feel free to correct, comment, expand. I'd like to be able to estimate gate counts of different designs for the purpose of architectural exploration.īelow is what I found out.

0 kommentar(er)

0 kommentar(er)